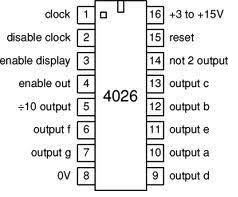

CD4026 Johnson Counter is a 5-stage Johnson decade counter with 10 decoded outputs (Q0 to Q9), an output from the most significant flip-flop (Q5-9), two clock inputs (CP0 and CP1) and an overriding asynchronous master reset input (MR).

The counter is advanced by either a LOW-to-HIGH transition at CP0 while CP1 is LOW or a HIGH-to-LOW transition at CP1 while CP0 is HIGH. When cascading counters, the Q5-9 output, which is LOW while the counter is in states 5, 6, 7, 8 and 9, can be used to drive the CP0 input of the next counter. A HIGH on MR resets the counter to zero (Q0 = Q5-9 = HIGH; Q1 to Q9 = LOW) independent of the clock inputs (CP0 and CP1). Automatic code correction of the counter is provided by an internal circuit: following any illegal code the counter returns to a proper counting mode within 11 clock pulses. Inputs include clamp diodes. This enables the use of current limiting resistors to interface inputs to voltages in excess of VCC.

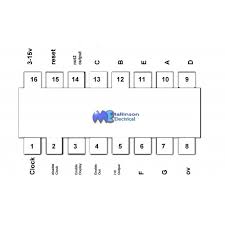

CD4026 JOHNSON COUNTER PINOUT:-

CD4026 JOHNSON COUNTER FEATURES:-

- Counter and 7-segment decoding in one package

- Easily interfaced with 7-segment display types

- Fully static counter operation: DC to 6 MHz (typ.) at VDD = 10 V

- Ideal for low-power displays

- Display enable output (CD4026B)

- “Ripple blanking” and lamp test (CD4033B)

- 100% tested for quiescent current at 20 V

- Standardized, symmetrical output characteristics

- 5-V, 10-V, and 15-V parametric ratings

- Schmitt-triggered clock inputs

- Meets all requirements of JEDEC Tentative Standard No. 13B, “Standard Specifications for Description of ’B’ Series CMOS Devices”

You can buy more product like this 7448 Decoder, 74138 Decoder etc.cheaper price from our shop.

Reviews

There are no reviews yet.