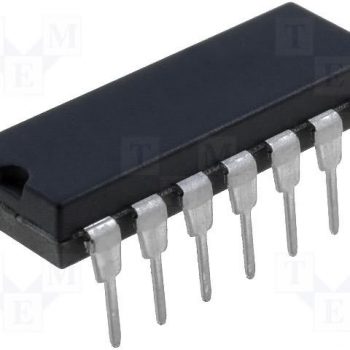

CD4018 N Counterof 5 Johnson-Counter stages, buffered Q outputs from each stage, and counter preset control gating. CLOCK, RESET, DATA, PRESET ENABLE, and 5 individual JAM inputs are provided. Divide by 10, 8, 6, 4, or 2 counter configurations can be implemented by feeding the Q\5, Q\4, Q\3, Q\2, Q\1 signals, respectively, back to the DATA input. Divide-by-9, 7, 5, or 3 counter configurations can be implemented by the use of a CD4011B to gate the feedback connection to the DATA input. Divide-by functions grater than 10 can be achieved by use of multiple CD4018B units. The counter is advanced one count at the positive clock-signal transition.. Schmitt Trigger action on the clock line permits unlimited clock rise and fall times. A high RESET signal clear the counter to an all-zero condition. A high PRESET-ENABLE signal allows information on the JAM inputs to preset the counter. Anti-lock gating is provided to assure the proper counting sequence.

Features of CD4018 N Counter

■ MEDIUM SPEED OPERATION 10 MHz (Typ.)

at VDD – VSS= 10V

■ FULLY STATIC OPERATION

■ STANDARDIZED SYMMETRICAL OUTPUT

CHARACTERISTICS

■ QUIESCENT CURRENT SPECIFIED UP TO

20V

■ 5V, 10V AND 15V PARAMETRIC RATINGS

■ INPUT LEAKAGE CURRENT

II

= 100nA (MAX) AT VDD = 18V TA = 25°C

■ 100% TESTED FOR QUIESCENT CURRENT

■ MEETS ALL REQUIREMENTS OF JEDEC

JESD13B ” STANDARD SPECIFICATIONS

FOR DESCRIPTION OF B SERIES CMOS

DEVICES”

Reviews

There are no reviews yet.